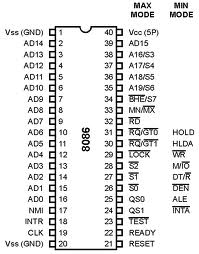

Hello friends, today we are going to discuss the 80186 microprocessor with integrated peripherals. The Intel 80186 is an improved version of the 8086 microprocessor. 80186 is a 16-bit microprocessor with a 16-bit data bus and a 20-bit address bus. It has a programmable peripheral device integrated into the same package. The instruction set of the 80186 is a superset of the instruction set of the 8086. The term super-set means that all of the 8086 instructions will execute properly on an 80186, but the 80186 has a few additional instructions. The following figure shows the block diagram and pin diagram of 80186. The CPU is divided into seven independent functional parts. 80186 internal block diagram 80186 68-pins pin diagram Functional parts of 80186 Microprocessor The Bus Interface Unit (BIU) Execution Unit (EU) Clock Generator Programmable interrupt controller Programmable Chip Select Unit (CSU) Programmable DMA Unit Programmable counter/timers The Bus Interface Unit ...

- Get link

- X

- Other Apps

Gr8 Website..

ReplyDelete2morrow is my microprocessor's paper and i m studying from here...

best notes ever:)

Easy to understand 8086 pins functions.

ReplyDelete